# Development of CMP (Chemical-Mechanical Polishing) Technology

by

Takashi Fujita / CMP Process Engineering Sec., CMP Dept., Semiconductor Equipment Div.

Naoyuki Kuratomi / CMP Process Engineering Sec., CMP Dept., Semiconductor Equipment Div.

Yoshiyasu Maeba / Manager, CMP Process Engineering Sec., CMP Dept., Semiconductor Equipment Div.

# Synopsis

The "Sparkle SP 4000" CMP system for interlayer film planarization has been developed and introduced to mass production fabrication. The "SP 4000" CMP system has the following performance and functions.

- -High throughput of 40 wafers/hour

- -Dry-in/Dry-out configuration by integrating cleaner

- -Process check function by including film thickness monitor

- -Clean room use

Recently, we began to develop a new CMP system for planarization of W (Tungsten) plugs. We describe our CMP technology and equipment in this paper.

## 1. Introduction

While increasing levels of ULSI integration results in interconnection lines becoming ever thinner, multilayer structures of interconnections are also being developed. In such multilayer interconnection structures, at present, the planarization process for each insulating layer has become an absolutely essential technology due to the problem of depth of focus in the optical lithography process. Table 1 shows typical multilayer interconnection surface planarization technologies1). The CMP (Chemical-Mechanical Polishing) technology has become the leading technology because of its superior planarization characteristics and simplicity of the process and is becoming an established replacement for the conventional techniques of etching<sup>2)(\*1)</sup>, reflow<sup>3)(\*2)</sup>,  $SOG^{4)(*3)}$ , etc.

At present, our CMP equipment has passed the development stage for application to device fabrications and is in the stage of mass production in which the process performance is being stabilized. This equipment is still considered to be in the development stage among the current semiconductor manufacturing processes, since there are many additional

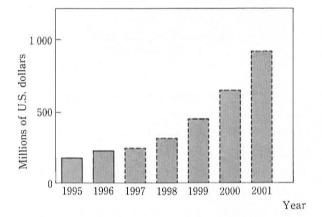

technical modifications and improvements that can be made by each manufacturer. Furthermore, the market is large and the market has still not become mature even when we consider the future prospects, so we can expect this field to be one in which considerable progress can be achieved in the future<sup>5)</sup> (Fig. 1).

Under these conditions, SMI's CMP equipment has completed the process development stage and is currently being carried over to mass production

- (\*1) Etch-back: Forming a coated film of photoresist, etc., on the insulation film covering the interconnection line steps, and planarizing the surface by etching under the conditions in which the etching speeds of the two are almost equal.

- (\*2) Reflow: Lowering the softening point by adding Phosphorus (P) or Boron (B) to the SiO<sup>2</sup> film which is the insulating film between interconnection layers, and planarizing the surface undulations by causing reflow during heat treatment.

- (\*3) SOG: Coating a solvent whose base is silanol, and planarizing the steps in the base material by heat treatment.

| Pl                   | ana       | rization<br>technology    | Cross sectional diagram               | Feature                                                                                           | Problem                                                                       |

|----------------------|-----------|---------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Local planarization  |           | Reflow                    | BPSG Metal line  Reflow               | Simple process<br>(CVD+Thermal process)                                                           | High temperature thermal process                                              |

|                      |           | SOG                       | CVD oxide film SOG  Cover film        | Simple process<br>(CVD+SOG+Etchback)                                                              | Crack generation<br>Combination with etchback<br>Stacked coverage             |

| Lo                   | Bias CVD  |                           |                                       | Simple process                                                                                    | Uniformity Particle generation Plasma damage                                  |

| Global planarization | Etch-back | No masking                | Resist CVD oxide film  Resist etching | Many process steps<br>Cover resist<br>Etchback<br>CVD                                             | Dry etch selectivity Incomplete planarity of cover resist End point detection |

|                      |           | Resist mask<br>patterning | Resist  Resist etching  Oxide etching | Complete planarization Many process steps Lithography CVD Resist patterning Cover resist Etchback | High cost Accurate alignment Dry etch selectivity End point detection         |

|                      |           | СМР                       | <b>→</b>                              | Complete planarization<br>Simple process                                                          | Pattern selectivity Post–CMP cleaning Contamination                           |

Table 1 Planarization technology of stack layered film

Fig. 1 Market forecast of CMP

plants, etc., and we are now making efforts to achieve stable mass production operation and improved performance.

In this paper we describe mainly the equipment configuration and its technical details, together with the fundamental technologies for application to mass production. In addition, some description is also given of the development of the metal CMP equipment.

# 2. Equipment Configuration

# 2.1 Outline of Equipment Configuration

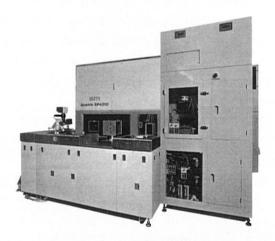

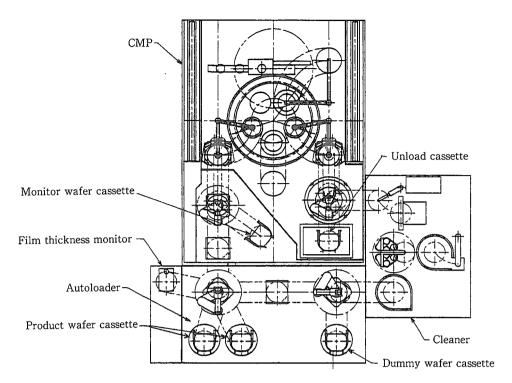

The external appearance of this equipment is shown in **Photo 1** and the equipment configuration is shown in **Fig. 1**.

The interior of the CMP equipment consists of five wafer stages so that five wafers can be polished

Photo 1 Photograph of CMP system

Fig. 2 Configulation of CMP system

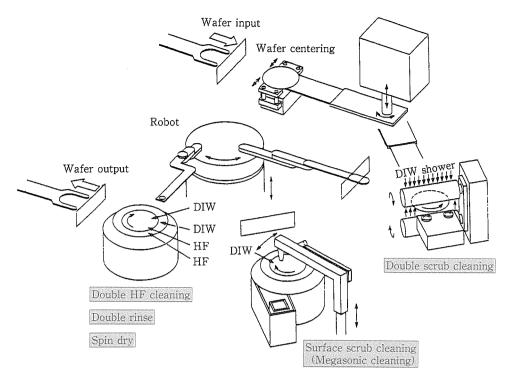

simultaneously. There are both two cassettes for products and one cassette for dummy wafers in the autoloader at the front of the equipment. Dummy wafers are loaded onto the wafer stages when there are fewer than five product wafers. The wafers are loaded sequentially by the robots from the left side of the equipment, then polished after the wafers are placed on the five wafer stages. When polishing is completed, the wafers are unloaded from the right side of the equipment. The polished wafers are first stored in the unload cassette, and then led to the cleaning unit one wafer at a time as required. The cleaning unit consists of three modules, the double side cleaning module that uses a roll brush, the surface cleaning module that uses a disk brush, and the chemical cleaning module that uses HF (hydrofluoric acid). The wafers are cleaned, rinsed, and dried by these modules, then stored back in the original cassette on the autoloader at the front of the equipment.

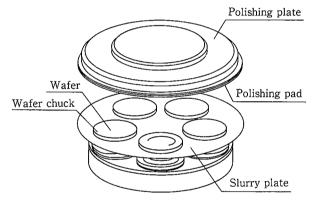

Figure 3 shows a schematic view of the polishing unit of the CMP equipment. The lower part of the equipment has the main table consisting of five wafer stages each designed to be in planetary motion. The top part of the equipment has the polishing plate with a polishing pad facing the wafers, and polishing is done by supplying slurry from the center of this polishing plate. This slurry is

Fig. 3 Schematic view of polishing unit

based on SiO<sub>2</sub> particles with the particle diameter being in the range of 0.03 to 0.05 m, and the solvent is made alkaline (pH of 10 to 11) so as to have chemical action. The polishing pad consists of a two layer structure. The surface layer is made of polyurethene type of resin which is hard and has high slurry retention. The inner layer is made of relatively soft rubber material. Because of this pad structure, while local planarization polishing is carried out on the one hand, the inner layer soft rubber becomes effective against the long range waviness on the wafer, and it is possible to remove the wafer surface uniformly because the pad confrorms to the wafer surface at all times.

#### 2.2 Conformation with Clean Rooms

Compared with other general semiconductor manufacturing equipment, it is most important factor that CMP equipment conforms to clean environment on designing CMP equipment. Since the polishing equipment uses slurry, it can easily become the source of particles and contamination. In particular, since the potassium K<sup>+</sup> ion component to maintain alkaline nature of the slurry has detrimental effects on semiconductor devices, all the device manufacturers are very reluctant to place the CMP equipment in the clean room of the semiconductor factory.

In our company's CMP equipment, in order to make the equipment conform to clean room conditions, we have long before proposed the concept of dry in and dry out<sup>(\*4)</sup> wherein the environments inside and outside the equipment are completely isolated and the CMP unit and the cleaning unit are integrated together.

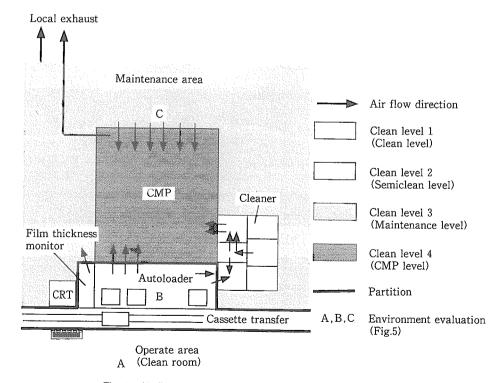

Figure 4 shows the environmental configuration of our CMP equipment. The maintenance side and the operation side of the equipment are completely isolated from each other by a partition, and the modules using the slurry are all placed on the

maintenance side. The cleanliness inside the equipment is divided into several classes, with the cleanest being the autoloader, then the cleaning unit, and the least clean being the CMP equipment. Air flow adjustment between these classes is used to prevent reverse diffusion of contamination, thereby maintaining the cleanliness of each section.

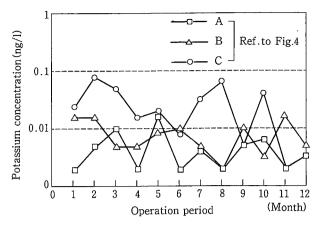

Figure 5 shows the results of evaluating the environment over a long period in a mass production factory. By adjusting the direction of air flow, the contamination rate of the environment at each position is reduced to less than 0.1ng/L thereby proving that the equipment conforms to clean room environments<sup>6</sup>.

(\*4) Dry In Dry Out: In general, in CMP equipment, the wafers are loaded in the dry condition, and are returned in the wet condition, but in this method, the wafers are unloaded in the dry condition by cleaning and drying the wafer.

Fig. 4 Air flow control in CMP room and environment keeping

Fig. 5 Environment evaluation at each location (Fig. 4) in CMP room

# 2.3 Film Thickness Measurement Unit

The film thickness measurement unit plays a very important role in increasing the product wafer yield by checking uniformity within wafer.

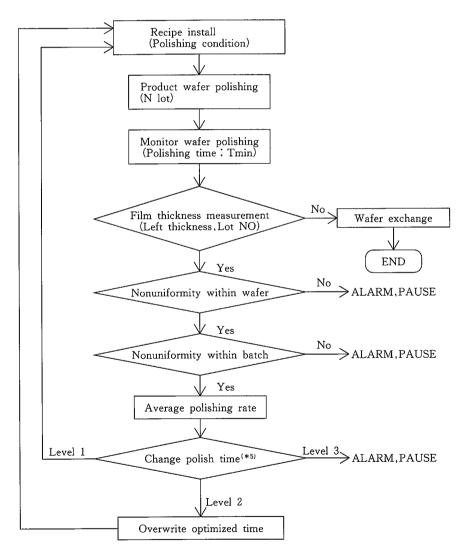

Figure 6 shows the polishing control flow diagram when the film thickness measurement unit is being used. The monitor wafer built into the unit is polished at regular intervals between product wafer lot processing, the film thickness after polishing at various locations of the wafer is measured by the film thickness measurement unit using optical interference measurement and the polishing rate and uniformity are evaluated. The processing conditions

(\*5) Changing polish time

| Polishing rate ta | rget R Level 1 | A <r<b< th=""><th>not change</th></r<b<>       | not change   |

|-------------------|----------------|------------------------------------------------|--------------|

| C A B I           | Level 2        | C < R < A, $B < R < D$                         | change       |

|                   | Level 3        | R <c, d<r<="" td=""><td>ALARM, PAUSE</td></c,> | ALARM, PAUSE |

Fig. 6 Flow diagram of polishing control using film thickness monitor

of the next product wafer lot are determined based on this evaluation. In SMI's CMP equipment, since the function of automatic compensation of polishing time is available, it is possible to obtain a stable amount of removal by polishing if there is some change in the polishing rate.

By using the film thickness measurement unit, it is possible to prevent in advance the generation of a large number of product defects due to excessive polishing or defects in uniformity, and hence it is possible to achieve stable operation during mass production.

# 3. Planarization Using CMP

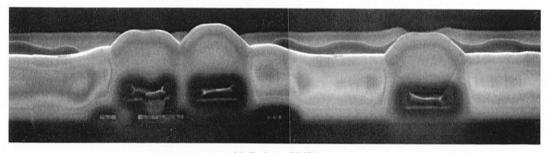

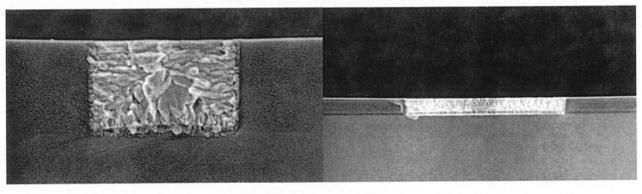

**Photo 2** shows examples of wafers before and after planarization by CMP. CMP makes it possible to achieve complete planarization that was not achieved by the other methods such as etch-back, and it is possible to obtain a flat and smooth surface with very little undulation. In addition, it is possible to return the surface condition to the original level of cleanliness by post-CMP cleaning.

#### 3.1 In-Situ Dressing Technology

One of the fundamental technologies that is a key to achieve mass production is the In-situ Dressing technology<sup>(\*6)</sup>.

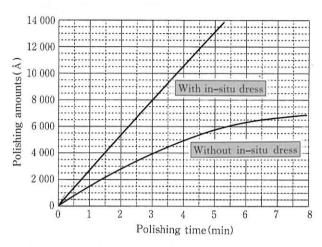

Figure 7 shows examples of dressing performance

Fig. 7 The difference of dressing performance with in-situ dress and without in-situ dress

in case that in-situ dressing is performed and not performed. When in-situ dressing is not performed, since the polishing pad reduces abrasive ability during polishing, thereby reducing the polishing rate, it is difficult to estimate the time required for obtaining the required polishing amounts. In contrast with this, when in-situ dressing is performed since the dressing of the pad (removal of blockage) is done while the polishing is being done, the polishing rate will not depend on polishing time but will be constant, thereby improving the controllability of

(\*6): In-Situ Dressing Technology: Technology of dressing the pad simultaneously with polishing.

(a) Before CMP

(b) After CMP

$3 \mu m$

Photo 2 Cross sectional view of planarization by CMP

polishing.

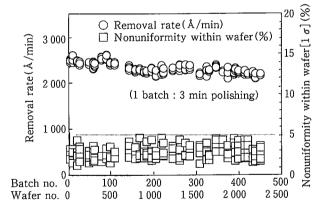

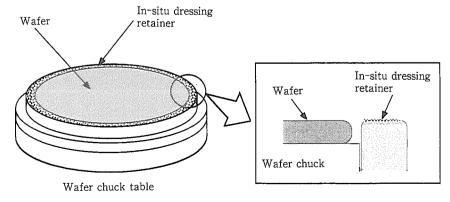

In SMI's CMP equipment, we have developed a dressing retainer with which the dressing of the pad is done simultaneously with polishing in addition to the original function of preventing over polish at the wafer edges (Fig. 8), With the dressing retainer, it is also possible to improve the controllability of the amount of polishing of the wafer edge by varying the height of the retainer relative to the surface of the wafer.

Figure 9 shows the stability of the polishing rate when continuous polishing is being done. It was possible to obtain a stable polishing rate: 2 000 Å/min or more for more than 2 000 batches (10 000 wafers) with an inter-batch rate stability: less than 5% (within 50 batches) and a surface uniformity (1): less than 5%. From this, it is possible to stabilize the polishing rate and uniformity of the polishing amount over a long duration, and hence it is possible to obtain stable performance suitable for mass production.

Fig. 9 Stability of removal rate and nonuniformity with dressing retainer

# 3.2 Cleaning Characteristics

The cleaning after CMP is a process that is essential for removing the slurry and contamination after polishing. The outline of the cleaning process is shown in **Fig. 10**. The cleaning process consists of the three processes the double side scrub cleaning process, the surface scrub cleaning process, and the HF cleaning process.

In the double side scrub cleaning process, the wafer is held between a pair of roll brushes and the slurry on both sides of the wafer is removed in this rough cleaning process by the rotation of the top and bottom rolls.

Next, in the surface scrub cleaning process, the small quantities of particles, that could not be completely removed in the double side scrub cleaning process, are removed by spraying a jet of DI water with ultrasonic waves and by scanning the disk brush.

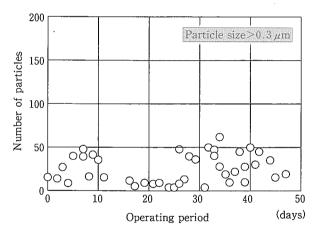

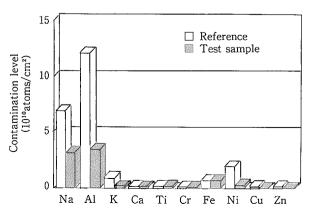

The final HF cleaning process is intended for removing the layer of the surface by HF (hydrofluoric acid) etching so as to remove the contamination components (mainly potassium components) that have adhered to the surface of the wafer during the polishing process and the subsequent scrub cleaning process. Figure 11 shows the result of particle count evaluation after post-CMP cleaning. The particle number after post-CMP cleaning has almost become stabilized at less than 50. Figure 12 shows the result of comparing the surface contamination of a wafer after post-CMP cleaning and a reference wafer for which CMP has not been carried out. This result shows that heavy metals and the potassium components contained in the slurry (K+) have almost completely been removed, and that there is no defect of wafer contamination by CMP.

Fig. 8 Dressing retainer structure around wafer chuck table

Fig. 10 Post-CMP cleaning process

Fig. 11 Particle evaluation after post CMP cleaning

Fig. 12 Contamination evaluation after post CMP cleaning

# 4. Development of Metal CMP Equipment for Planarizing Tungsten Plugs

While we carried out the development of CMP equipment in our company for the conventional insulating films, there has been an increasing demand for the application of CMP for the planarization of tungsten plugs, and we have developed the metal CMP equipment SP5000 for planarizing tungsten plugs. The equipment configuration for the metal CMP is equivalent to the one for the conventional CMP except for slurry system. Acidic slurry is used for the metal CMP instead of alkaline slurry which is used for conventional CMP. Therefore corrosion resistance of the materials is provided for slurry line in the metal CMP. For the pad, we are using the same polyurethene foam as the one used for polishing silicon dioxide films.

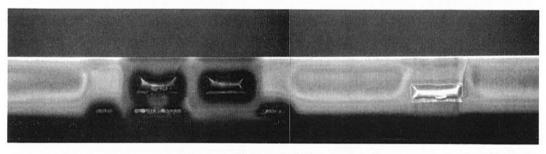

**Photo 3** shows examples of planarizing tungsten plugs. The surface of tungsten and oxide films are almost uniformly planarized for hole diameters from 1 up to 5, and it is possible to obtain a flat and smooth surface without any dishing<sup>(\*7)</sup>.

### **Technical Explanation**

$0.5 \mu m$

$3 \mu m$

Hole diameter :  $1 \mu m$

Hole diameter: 5 μm

Photo 3 Cross sectional view of W plug planarization

# 5. Conclusins

It has been possible to introduce CMP equipment for mass production in the market, and to get them introduced in mass production factories after developing the processes. In the future, customer requirements are likely to become far more severe due to the increasing levels of integration in LSIs, and we are planning to make additional modifications and improvements in the equipment and processes. In addition, at present, we have received orders for CMP system( $\phi$ 8") not only within Japan but also from abroad. On the other hand we are developing newly metal CMP equipment and CMP equipment for 12" diameter wafers.

(\*7) Dishing: The phenomenon of dish shaped recession appearing near the interconnection parts due to a difference in the polishing speeds of materials.

-----

Takashi Fujita

CMP Prosess Engineering Sec., CMP Dept., Semiconductor Equipment Div.

Phone: 06 (466) 6249

#### References

- T. Kikkawa, 22th Thinfilm Surface physics seminar., 100 (1994)

- A. Shiltz and M. Pons, J. Electrochem. Soc., 135, p.1019 (1988)

- 3) A. N. Saxena and D. Pramanik, Solid State Technol, 11, p.45 (1986)

- 4) P. L. Pai, A. Chetty, and R. Roat, J. Electrochem. Soc.,

134, 2829 (1987)

- 5) Dataquest p.28 (January 1997)

- 6) N. Takenaka : 2 nd International CMP Symposium (1996) p.284

- 7) N. Takenaka: 2nd International CMP Symposium (1996) p.285

- 8) T. Fujita: Proceedings of JSPE spring meeting 197 (1997)